### **Design of Synchronous Counters**<sup>1</sup>

V1.2 (2025 – fixed equations in step 5)

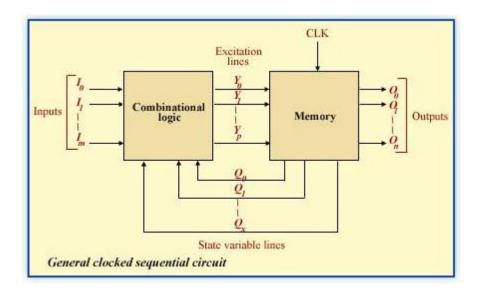

This section begins our study of designing an important class of clocked sequential logic circuits-synchronous finite-state machines. Like all sequential circuits, a finite-state machine determines its outputs and its next state from its current inputs and current state. A synchronous finite-state machine changes state only on the clocking event.

Due to time, we will not be covering finite state machine inputs, but these would be used to control the state machine. Examples would be count up / count down inputs, hold, change of sequence, etc.

#### **Counter Design Procedure**

- Describe a general sequential circuit in terms of its basic parts and its input and outputs.

- Develop a state diagram for a given sequence.

- Develop a next-state table for a specific counter sequence.

- Create a FF transition table.

- Use K-map to derive the logic equations.

- Implement a counter to produce a specified sequence of states.

.

<sup>&</sup>lt;sup>1</sup> Floyd Digital Logic Chp 8

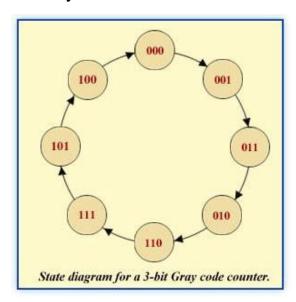

# Design Example #1: 3-bit Gray code counter

# **Step 1: State Diagram**

State Diagram for a 3-bit Gray code counter:

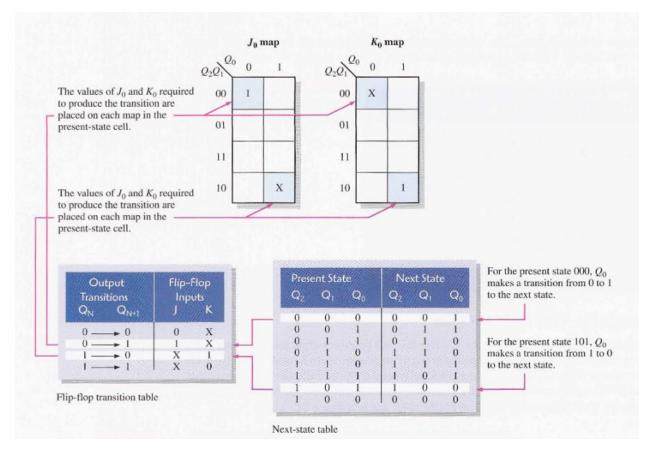

**Step 2: Next-State Table**

Next state table for a 3-bit Gray code counter

| Present State |         |              | Next State |       |       |

|---------------|---------|--------------|------------|-------|-------|

| $Q_2$         | $Q_{I}$ | $Q_{\sigma}$ | $Q_2$      | $Q_i$ | $Q_o$ |

| 0             | 0       | 0            | 0          | 0     | 1     |

| 0             | 0       | 1            | 0          | 1     | 1     |

| 0             | 1       | 1            | 0          | 1     | 0     |

| 0             | 1       | 0            | 1          | 1     | 0     |

| 1             | 1       | 0            | 1          | 1     | 1     |

| 1             | 1       | 1            | 1          | 0     | 1     |

| 1             | 0       | 1            | 1          | 0     | 0     |

| 1             | 0       | 0            | 0          | 0     | 0     |

**Step 3: Flip-Flop Transition Table**

Transition table for a J-K Flip-Flop

| Output Transitions |          |           | Flip-Flop Inputs |     |  |

|--------------------|----------|-----------|------------------|-----|--|

| $Q_{v}$            | - 1      | $Q_{N+1}$ | I                | K   |  |

| 0 -                | +        | 0         | 0                | X   |  |

| 0 -                |          | 1         | 1                | X   |  |

| 1 -                | +        | 0         | X                | 1   |  |

| 1 _                |          | 1         | X                | 0   |  |

| 2,: prese          | est etal |           | : next sta       | idi |  |

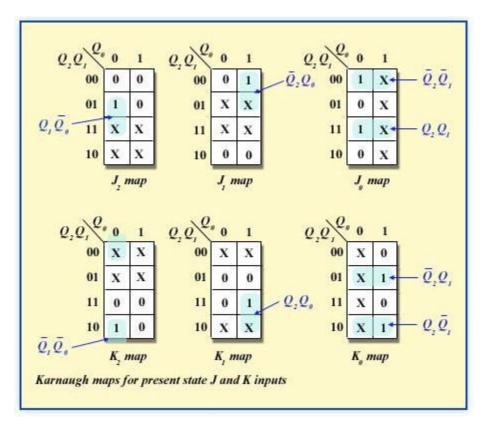

#### Step 4: Karnaugh Maps

The following diagram shows the steps to create separate next states of separate J and K from the current states of J and K.

Karnaugh maps for present-state J and K inputs for the 3-bit Gray code counter.

**Step 5: Logic Expressions for Flip-flop Inputs**

The next-state J and K outputs for a 3-bit Gray code counter.

$$J_{0} = Q_{2}Q_{1} + \overline{Q}_{2}\overline{Q}_{1} = \overline{Q_{2} \oplus Q_{1}}$$

$$K_{0} = Q_{2}\overline{Q}_{1} + \overline{Q}_{2}Q_{1} = Q_{2} \oplus Q_{1}$$

$$J_{1} = \overline{Q}_{2}Q_{0}$$

$$K_{1} = Q_{2}Q_{0}$$

$$J_{2} = Q_{1}\overline{Q}_{0}$$

$$K_{2} = \overline{Q}_{1}\overline{Q}_{0}$$

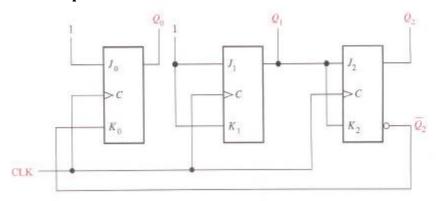

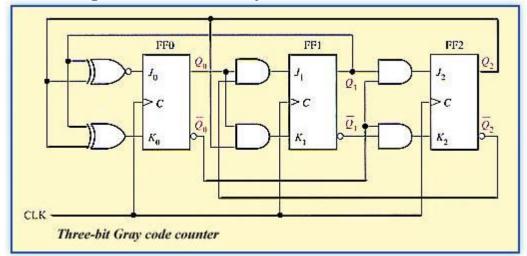

### **Step 6: Counter Implementation**

The hardware diagram of the 3-bit Gray code counter

• There are many more examples for the design of synchronous counter. These can be found in any digital network related textbooks.

# **Design Example #2**

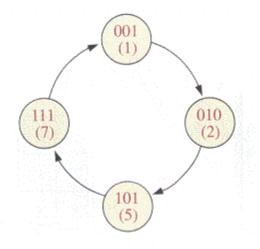

Design a counter with the irregular binary count sequence shown in the state diagram of Figure 4.1.

**Step 1: State Diagram**

**Step 2: Next-State Table**

| Present State |       |       | Next State |       |       |

|---------------|-------|-------|------------|-------|-------|

| $Q_2$         | $Q_1$ | $Q_0$ | $Q_2$      | $Q_1$ | $Q_0$ |

| 0             | 0     | 1     | 0          | 1     | 0     |

| 0             | . 1   | 0     | 1          | 0     | 1     |

| 1             | 0     | 1     | 1          | 1     | 1     |

| 1             | 1     | 1     | 0          | 0     | 1     |

#### **Step 3: Flip-Flop Transition Table**

Transition table for a J-K Flip-Flop

| Flip-Flo<br>J | p Inputs<br>K                     |

|---------------|-----------------------------------|

| 0             | X                                 |

| x             | î                                 |

|               | Flip-Flo<br>J<br>0<br>1<br>X<br>X |

$Q_s$ : present state,

$Q_{n+j}$ : next state

X : "don't care"

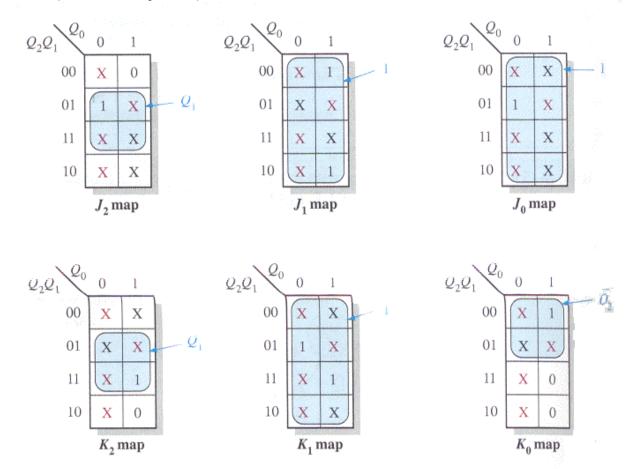

#### Step 4: Karnaugh Maps

Note: "don't cares" can be placed in the cells corresponding to the invalid states of 000,011,100 and 110 (as indicated by red X)

### **Step 5: Logic Expressions for Flip-flop Inputs**

The expression for each J and K input taken from the maps is as follows:

$$J_0 = 1, K_0 = Q_2$$

$$J_1 = K_1 = 1$$

$$J_2 = K_2 = Q_1$$

# **Step 6: Counter Implementation**